ң�뵱�꣬Ӣ�ض���Intel����ʼ��֮һ��ǡ�Ħ��������Ħ�����ɣ�Ϊ�뵼����ҵ��չָ����һ������������������Ͼ�������1965������������ʮ���꣬�ڵ����������������ޣ���ҵĦ�������Ż����������Ե���Ħ��������������

������ʵ���ǣ����ڵ�ת��Խ��Խ���ˣ���������Խ��Խ���ˡ����ں�Ħ��ʱ������ҵֻ��ĬĬ��������ıƽ��������Ӣ�ض�Ϊ���߽���Ħ������̽���е��¹յ㣬����װ������

��װ������ΪĦ�����ɵ��¹յ�

Ħ�����ɵ�����ʲô����װ������Ħ�����ɵ�����ʲô��ϵ����������ϸϸ������1965���������ǡ�Ħ����ʾ���ɵ�·�Ͽ����ɵ�Ԫ��������Լ18���±������һ��������1975�꽫��һ������Ϊ��λ���оƬ�ϵľ��������ÿ������ʵ�ַ�����

����Ħ������������ʷ���þ���ܹ�����һ�����̣�ͻ����������Ҳ���Ⱥ������ƿ�������������ı��ǰ뵼����ϵ����ƣ��ɴ���ҵ�����˵绯ѧ��ͭ�ͻ�еƽ�滯��˫��Ƕ�ṹ�����������������豸�������ƣ�Siդ����SiO2դ������ʲ��ϱ�����դ����K�����ȡ�����ٵ�193nm�ڵ����ϣ��ܵ���̼������ƣ���ҵ��̼������Է�����Ƴ̽ڵ�45nm-32nm�²����˽�û���ա�16nm-10nm�²����˶����ع�ա�7nm-5nm�������˼������ߣ�EUV�����ա�

��ˣ����Կ�����Ϊ������Ħ�����ɣ�ר�ҽʾ���֭�뾡���ְ취�������ı�뵼����ϡ��ı�����ṹ�������µĹ��ա������ɷ��ϵ��ǣ�Ħ�������ڽ������Ż���10nm��7nm��5nm����оƬ�Ƴ̽ڵ�Խ��Խ�Ƚ���оƬ����ƿ��ҲԽ��Խ�ѿ˷���

��ˣ�ҵ��ר��ָ���˺�Ħ��ʱ���Ĺ輼���ķ�չ����һ���Ǽ������á���-��ŵ��������ʽ��ͨ���ı�ṹ�γ�����������ʹ��Ħ�������ܹ���������һ�����Dz�������ģʽ�����˼ܹ�������3D��װģ����Ԫ���ԣ���������һ��ļ��㣬���ּܹ��������ģ���ӵ�в����ԡ�

����Ħ�����ɵġ���ʵ��˿��Ӣ�ض���һֱ����ĬĬ���ո�ǡ�Ħ������·�߷�չ��ͨ����̽��ͷ�ķ�չ�������ܿ���ʲô��

���ڣ�Ӣ�ض���������IDM 2.0ʱ������ʱӢ�ض�CEO���ء�����������Ӣ�ض������Ŵ�������IFS�����ϸ��£����ء���������Ͷ���߱�ʾ���������Ѿ�����DZ�ڵĴ����ͻ��Է�װ�����dz�����Ȥ����

Ӣ�ض�Ժʿ����װ�о���ϵͳ��������ܼ�Johanna Swan��ʾ����װ��δ��˱������������ݶ��壬��װ��Χ��һ�������辧Ƭ����ǣ����Ա�����Ƭ�������Ӱ�죬ʵ��ɢ�ȣ��ṩ��Դ����������������������������������װ�����������ⲿ���ӵģ���ͬʱ�����Ż��ڲ����ܣ�һֱ�ﵽ�������һ����

��ô��װ������Ħ��������ʲô��ϵ�أ�Swan��ʾ����װ����һ����ʯ�ǡ��������ܻ����������λ������ܡ���

����˵����װ�ܹ�����оƬ������࣬�������ܶȡ�������ܶ�Խ��ʵ����Ҳ�����ŵ�λ����Ͼ��������Խ�ܡ�����˵����װ��Ȼ��Ħ������û��ֱ�ӹ�������ȴ��Ӱ����Ħ�����ɵķ�չ��

��Ŀǰ��˵��Ӣ�ض�����оƬ�ӵ�һоƬ��ֳ�Ϊ����СоƬ��Ȼ�����������ϣ������Ӣ�ض���СоƬChiplet 2.0�ļ�������ˣ������ķ�ʽ֮�£����ڷ�װ�ͻ�������Ҫ�������ߡ�

����֮�⣬��Ҫע����ǣ�Ӣ�ض�������������̬оƬ��Loihi�����ò�Ʒ��ȴ�ͳ������ܹ���˵����ȫģ�����ڴ�ʹ���֮��Ľ��ޡ�ʵ���ϣ���Ҳ��Ӧ��֮ǰҵ��ר�ҵķ�����֮�����ܹ�ģ����Ԫ���ԣ��������Ƚ���3D��װ����������ڴ˷����װҲ�����˴���

Ӣ�ض��ķ�װ�����������µ�����

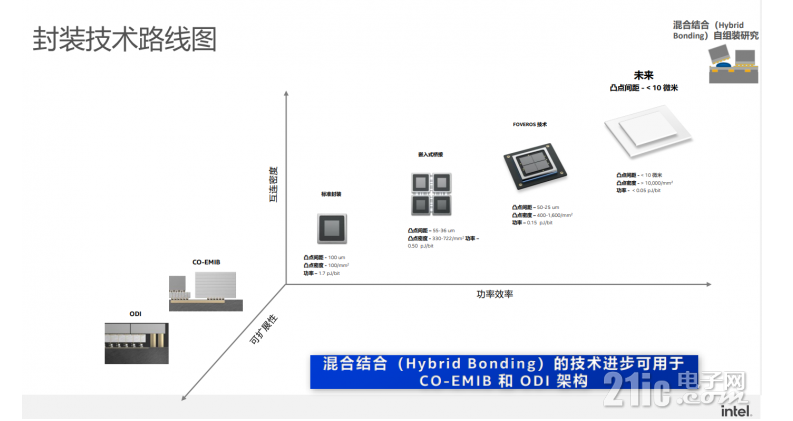

��ô��ͷӢ�ض��ķ�װ��������η�չ�ģ�����Swan�Ľ��ܣ��ӱ���װ��EMIB��Ƕ��ʽ���о�����Žӣ��ٵ�Foveros�������100��m������50-25��m��չ��δ����Ӣ�ض�Ҫ����С��10��m�����ࡣ

��Ӣ�ض����ܣ�EMIB��Ӣ�ض���һ��2.5D���ܶ���������ͨ��EMIB��������ʵ�ָ��õĵ����ܶȡ�ͨ�������н������װ�ڣ�����ɽ��оֲ����ܶȲ��ߣ�����ȫ��оƬ�ĸ��ܶȲ��ߡ�����EMIB�������ɽ�����FCBGA���л���װ����IO��������256-1024 IO/mm/�㡣������ܹ�ʵ��55-36��m�������ÿƽ������330-722/m�O�����ܶȣ����ʿ��Կ�����0.5pJ/bit��

Foveros����һ��3D���ܶ��������������ڴ˻����Ͻ�����������ƣ�IO���������Դﵽ��400��10000IO/mm²��������ܹ�ʵ��50-25��m�������400-1600/m�O�����ܶȣ����ʿ��Կ�����0.15pJ/bit��

��ȻӢ�ض���Ŀ����10��m���£���ô���ʵ�֣����ǡ���Ͻ�ϡ���Hybrid bonding������ȥ��ڶ����ȣ�������IJ���оƬ�Ѿ���Ƭ�����øü��������ܹ�ʵ��10��m�����Ը��������ʹ�����ܶȴﵽ10000/m�O�����ʿ�����0.05 pJ/bit�����ң���Ͻ�ϼ�������ʹ���뾧Ƭ����Բ��Ҳ����ʹ���뾧Բ����Բ��

Swanǿ����Hybridbonding�ܹ�ʹ��оƬ��ʵ�ָ��������Ӣ�ض��ܹ��ṩ��С�����ĵ�·��Ҳ���������루fan-in�����ȳ�(fan-out)�����˸��ĵ�·��Ӣ�ض�����ʹ�ø��͵ĵ��ݣ��Խ���ͨ���Ĺ��ʡ�

����Ħ�����ɵļ����ƽ���оƬ�ijߴ���ܻ���Խ��ԽС��Ϊ�˱�֤�㹻�Ĵ���������Ҫ�ڵ������¹�������СоƬ�ߴ���Խ��ԽС����ʵ���ż����Խ��Խ�̣���ͳ���ں��ϵļ����Ѿ���Ҫ�������ˣ������ΪʲôӢ�ض�Ҫʹ��ȫ�µļ�����Ͻ��Hybrid bonding��װ��

��ôHybrid Bonding����Foveros��ʲô����ƾʲô��Ͻ�Ϸ�װ���ܼ������ࣿ����Swan�Ľ��ܣ��辧Ƭ�ֲ��ڶ����͵ײ����м����Ǵ����ϵ�ͭ����Ӣ�ض������ľ��ǽ����Ǹ�����һ��ͻغ����������¡���ЩоƬ֮���в�ͬ���¶ȣ���Ҫ�ۻ����ϣ��������һ�𣬽������Ӻͻغ���������������ͷ������֮���еײ���佺�ķ��䣬������л�����֬�Ĺ����ģ��֮����ȷ�������ܷⲢ�ܹ���ɷ��벢��װ��

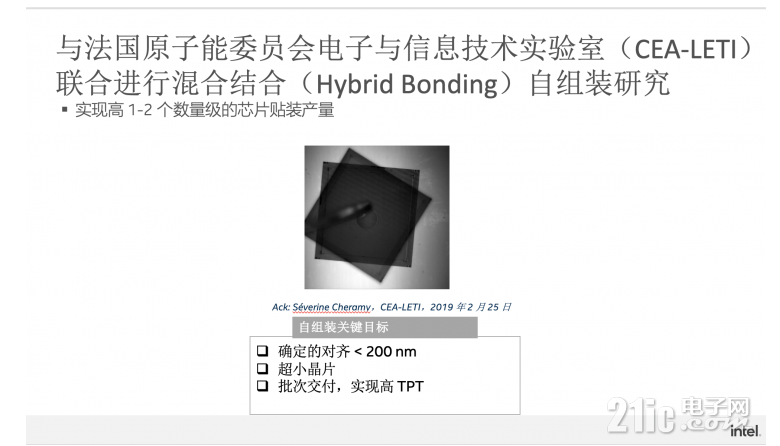

Hybrid Bonding��Foveros�ĺ��ӹ��ղ�ͬ���뺸�Ӽ����෴����Ͻ�ϼ���ʹ����ʵ�оƬ�dz��⻬����������ͻ�����㣬����ʵ���ϻ��������ݡ������û�Ͻ�ϼ������������������һ��ʱ�����������¶ȣ�����������ճ�������������������ź��������¶Ȳ������˻�ͭ����ʱ�����ͣ��Ӷ��γɵ������ӡ�Swanǿ�������Ƿdz����õģ���Ϊ�����ɻ�ø��ߵ�����������

�������������Խ������С��10�����¡�����ʹ����Ŀǰ����Щ�ӿ�֮�����˱ȵײ����ͽ��ܵ�ͭ�ܶȸ��õ������ܡ���������ʹ�û�Ͻ�ϼ���ʱ������Ҫһ���µ����졢���Ͳ��Է�������Swan����˵��

ʵ���ϣ����ָ�С�ļ���ľ����������ܹ��������༼���Ľ�����SwanΪ���߽��ͣ�Ӣ�ض�����2020��ܹ�����չ����Ƭ�ķֽ⼼����Ӣ�ض������ΪGPU��CPU��IO��оƬ�����飬�����Ϳ������õ�����IP�ĸ��ü��ٿ���ʱ���оƬȱ�ݡ�

��Hybrid Bonding��������֮�ʣ��ܹ���Ч�������࣬ʵ�ָ��ߵ����ܶȺ��͵Ĺ��ġ�

���������ں���ת��Hybrid Bonding����Ȼ��Ҫ�����һ����ս����Swan̹�ԣ�ͻȻ������ô�����飬�������������������ͬ���ٶȽ��У����������и���ľ�Ƭ��Ҫ���á���

�������ڿ��ǵĽ��������������װ�����dz�֮Ϊ����װ����Swan����Ϊ���߽��ܡ�

Ŀǰ����װ�Ѿ���һЩ�о��ڽ����У�Ӣ�ض����ڻ�����CEA-LETI�����о���ּ��һ���ܹ����ø������Ƭ��ͬʱȷ����ʹ�÷dz�С�ľ�Ƭ���ٷ��á�Ŀǰ��˵����Ͻ������װ�ѳ�ΪӢ�ض��о����ص㣬�������о�·��ͼ֮�С�

Ӣ�ض��ķ�װ��������λһ���

�����ڹ���Ч�ʺͻ����ܶ��ϵ�������Ӣ�ض�������װ�����ֳ�����չ�����ά�ȡ���һά��֮�ϣ�����Co-EMIB��ODI����������

����֮ǰӢ�ض��Ľ�����˵��Co-EMIB���ں�EMIB������Foveros������һ�ַ�װ�����ں�2.5D��3D�ļ����������EMIB�����ˮƽ����Foveros����ɴ�ֱ������ôCo-EMIB������λһ��ļ����������ķ�װ��ʽ���ܹ��������Ӹ��ܶ�����Ч����

����˵������չ��Co-EMIB�ļ����Ƿ������з�װ��ʽ���Ƶ�ƽ̨��Ҳ��2.5D��3D��װ������ײ���ڡ����Է������ƵĻ㼯�ء�

ʵ���ϣ��г��������£�����Ҳ��ʼ��2.5D��3D��װ����������ϡ�Swan��Ϊ��������ϵ����ƽ�����������ȥ���������������ܹ�Ϊ��Ʒ��������Ļ���Ͳ��컯���ơ�

Ӣ�ض�����2.5D��3D��װ��ϵijɹ�����Ponte Vecchio���ò�Ʒ��λ�ڳ��������������������������ء�������¶����Ϣ��Ponte Vecchio������Ӣ�ض��������Ƚ��ķ�װ���գ�����ܹ�ģͻ��1000�ڣ����ɼ��ɶ��47�Ų�ͬоƬģ�飬�ṩǧ���ڴ�(PFlops)�ļ���������

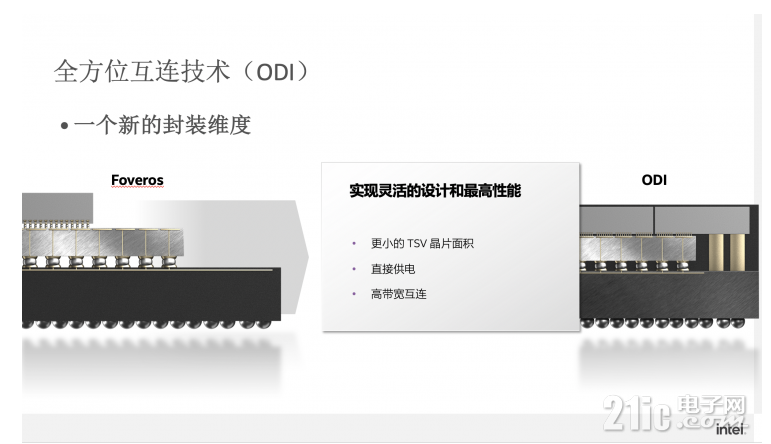

��һ���ľ߿���չ�Եļ�������ODI��ȫ��λ���������������ݴ�ǰ�Ľ��ܣ��ڳ���ĵ��ӷ�ʽ�£�����Ļ�����Ƭ�����ǽϴ�ģ���Ҫ����������ӵ�����СоƬ���ܺ͡�ͨ��ODI�������Ըı���һ�㣬����֮����Խ��и��õ�Э�������ҿ��������������ͳһ��

Ӣ�ض���ȫ��ȫ��λ����������ODI��Ϊ��װ��СоƬ֮���ȫ��λ����ͨ���ṩ�˸��������ԡ�����оƬ������EMIB������һ��������СоƬ����ˮƽͨ�ţ�ͬʱ��������Foveros������һ����ͨ����ͨ�ף�TSV��������ĵײ���Ƭ���д�ֱͨ�š����⣬���ַ��������˻���Ƭ������Ĺ�ͨ��������Ϊ��Դ������ͷ��˸������������Ż�����Ƭ�ijߴ硣

ODI������һ���Ż���ͨ������ ODI ��װ������Ϊ�ͻ��������ඨ�ƻ��ķ�����

�ܽ�

��������Ӣ�ض���һ��װ���������оƬ��������������С�ı䡱���������赭д�ˡ���Swan����˵��

ͨ�����ĵ�����������ʵ����Ӣ�ض��ƽ����ֽ��װ�����������ﵽ�˾���ܵļ���ʹ�ó�ΪĦ������̽�����¹ؼ�������δ���¼ܹ�ϢϢ��ء�

�Դ�Ӣ�ض��Ƴ�Ӣ�ض���������IFS�����ֽ�ķ�װ��������������DZ�ڴ����ͻ�����ʹӢ�ض��ܹ��ṩ�������Ȳ�Ʒ��

�ڱ��߿�������Ħ�������ƽ�����֮ʱ��δ�����ɵ�·��ҵ�ں�Ħ��ʱ������Ҫ�����ڰ뵼����ϡ��ṹ���գ���Ҫע���װ���������Ծ���ܵ�Ӱ�죬��������δ���ƾֵĹؼ���

�ڵ�һ��7nmоƬ����֮��ÿ���Ƴ̵���߶�������Ħ�����ɽ��������ԡ�������ҵ��������¶һЩ��1nm�Ƴ̺���о��ɹ���

�������Ҫ����һ��dz�ϲ���Ļ�����ÿһ������Ħ�����ɵļ��ޣ����Ƕ��ܳ���ɽǰ����·���ҵ��µķ���ͷ�չ�ռ䣬Ħ�����ɲ�����ȥ�������Ļ���ֻ�Ǹ�����ʱ��ǰ���Ĺ�˾����