原本人类专家需要花费数周时间完成的芯片布局设计,目前通过一种深度强化学习方法,平均6小时内就能完成这个过程,速度超28倍。

6月10日,来自美国加州谷歌研究院(Google Research)的Azalia Mirhoseini、Anna Goldie等在国际顶级学术期刊《科学》(Science)发表的一篇论文《一个快速芯片设计的布图布局方法》(A graph placement methodology for fast chip design)中指出,机器学习工具可以极大地加速计算机芯片设计。

Barrett et al.

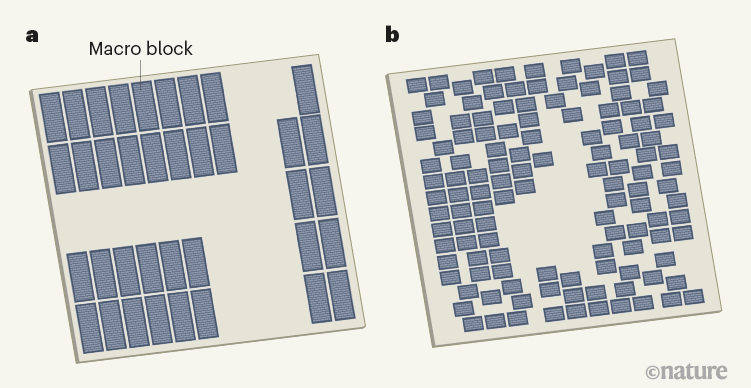

微芯片的面积约为几十到数百毫米平方,在一块指甲盖大小的硅片上排列并互连了数十亿个晶体管。每个芯片可以包含数千万个逻辑门,称为标准单元,以及数千个存储块,称为宏块或宏。单元和宏块通过数十公里的布线互连以实现设计的功能。

芯片中单元和宏块的位置对设计结果至关重要。它们的位置决定了布线必须跨越的距离,从而影响能否在组件之间成功布线以及信号在逻辑门之间传输的速度。

美国加州大学圣迭戈分校的Andrew Kahng在《自然》发表的《人工智能系统在设计微芯片平面图方面胜过人类》(AI system outperforms humans in designing floorplans for microchips)中写道,微芯片设计的成败在很大程度上取决于“布局规划” (floorplanning)和放置的步骤。

这些步骤决定了内存和逻辑元件在芯片上的位置,相应的位置会极大地影响芯片设计是否能够满足处理速度和电源效率等操作要求。到目前为止,尤其是在布局规划方面没有任何自动化尝试。因此,它常常是由专业的人类工程师在数周或数月内反复和艰苦地执行的。在芯片的设计过程中,全局布线是最复杂和耗时的阶段之一,也是决定芯片整体性能的关键。

谷歌的研究团队发现,机器学习工具可以用来加速“布局规划”的流程。该研究团队将芯片的布局规划部分设计为一个强化学习问题,并开发了可完成可行芯片设计的神经网络。他们训练了一个强化学习智能体,这个智能体会把布局规划看作一个棋盘游戏:元件是“棋子”,放置元件的画布是“棋盘”,“获胜结果”则是根据一系列评估指标评出的最优性能(评估基于一个包含1万例芯片布局的参考数据集)。

作者指出,这种方法能在6小时内设计出与人类专家不相上下或是更好的可行芯片布局。

人类设计的微芯片平面图与机器学习系统生成的平面图不同

Andrew Kahng认为,“开发出比当前方法更好、更快、更省钱的自动化芯片设计方法,有助于延续芯片技术的‘摩尔定律’ 。”摩尔定律指每块芯片的元件数量大约每两年会翻一番,这种进步速度相当于芯片上组件数量每周增加约1%。“因此,无法自动进行布局规划是有问题的――不仅因为相关的时间成本,还因为它限制了芯片开发计划中可以探索的解决方案的数量。”

他还表示,研究团队的布局规划方案已经被应用在谷歌的下一代AI处理器的设计上,这也显示出其可应用于大规模生产。除了加速芯片设计外,该研究或也能用于优化城市规划、疫苗测试等。