加速PCIe 5产品设计和测试

作者:是德科技设计工程软件全球市场营销总监Roberto Piacentini Filho

关键要点

●伴随AI和数据中心领域对硬件的需求水涨船高,PCIe 5.0标准成为一个重要的里程碑。

●尽管PCIe 5.0主要沿用了与4.0相同的技术,但一些巧妙的优化措施使其能够有效地将最大数据传输速率提高四倍。

●PCIe 5.0的设计和合规具有挑战性,因此需要非常先进的硬件和软件解决方案来简化流程。

PCIe(Peripheral Component Interconnect Express)是为现代服务器和计算机添加显卡和网卡等关键外设的首选总线,也是推动生成式AI、全球超大规模数据中心以及其他许多领域发展的重要硬件组成部分。

此篇是德科技文章将介绍PCIe 5的基础知识、应用、挑战以及简化设计和测试的解决方案。

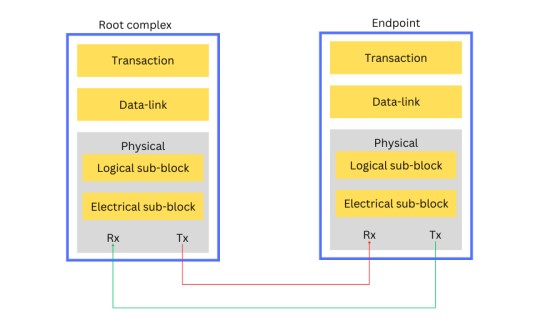

图1:PCIe 5协议层

PCIe 5.0是PCIe规范的第五代版本,也是用于将外围设备连接到服务器和计算机的最流行的互连标准。PCIe标准确保来自不同供应商的主板、显卡、以太网卡、Wi-Fi卡、存储设备和其他外围设备在集成到服务器或计算机时可以无缝互操作。

构成PCIe 5.0标准的逻辑子块如上图所示。

在数据传输方面,PCIe 5.0是一种由多个并行通道组成的串行接口。每个信号通道将数据以每次一个比特的串行方式进行传输。不过,所有通道可以同时进行传输和接收,以提高净吞吐量,其模式有点像并行总线。

本节将探讨一些推动PCIe Gen 5及以上版本采用的关键用例。

AI将成为PCIe 5及以上版本的主要应用场景。特别是大型生成式AI模型(参数范围从200亿到超过5000亿),因为它们需要将数据从系统内存或存储通过互连总线以尽可能高的容量和速度输送到AI加速器。服务器和个人使用的AI加速器都能从Gen 5的高带宽中获益匪浅。

PCIe 5.0是用于超大规模数据中心的关键组件,能够支持现代AI、大数据和高性能计算等应用。PCI Express 5还支持更快的技术,例如:

●下一代以太网:PCIe 5可以支持数据中心等应用中的400 GE网络接口卡和交换机。

●高速存储:企业级存储技术,如通过光纤信道的NVMe SSD,都依赖于PCIe 5。将各种存储设备连接到主板和处理器的存储控制卡和芯片组依赖于PCIe,并可受益于PCIe 5的速度。此类存储技术包括串行连接的小型计算机系统接口(SAS)和串行高级技术附件(SATA)。

●加速卡:用于AI或图形工作负载的现代加速卡,如GPU和TPU,都可受益于PCIe 5及更高标准。

PCIe 5通过直接内存访问(DMA)技术在显卡(如Nvidia GeForce RTX GPU)和系统内存之间实现了高速数据传输,为游戏玩家、图形专业人员和视频编辑人员带来裨益。

此外,PCIe Gen 5 SSD和M.2 NVMe控制器还能提升系统性能,确保在使用现代大核高性能CPU和最新的DDR5系统内存时,存储不再成为瓶颈。

PCIe 5.0的主要性能提升有哪些?

PCIe 5.0的一些关键性能如下。

PCIe 5.0每个信号通道在每个方向的最大带宽可达32 GT/s。每次传输涉及一个方向上的一个信号转换,这也意味着每次信号转换代表着传送了一个比特位的数据。因此,每个PCIe通道在每个方向的有效带宽为32 Gbps。

对于16通道双工接口(如典型的GPU x16插槽),网络带宽为128 GB/s。

典型以太网卡的八通道(x8)双工PCIe插槽可提供64 GB/s的网络带宽,足以满足400GE网络所需的50 GB/s吞吐量。

PCIe 5采用的非归零(NRZ)编码以16 GHz的频率运行,是PCIe 4.0 8 GHz频率的两倍。在这一较高频率下,必须有效应对信道插入损耗造成的更大信号衰减。

因此,PCIe 5.0采用了新的均衡和其他技术,以在更高速度下保持信号完整性。它实现了更好的性能、更高的可靠性和更低的错误率,而且还有助于延长电缆长度。

降低错误率

PCIe 5规定误码率(BER)低至10-12,总信道插入损耗预算仅为36 dB。为了应对可能出现的更多突发错误,PCIe 5要求在发射机上进行预编码。

由于带宽更高,PCIe 5.0可以同时支持更多设备,而不会出现任何瓶颈。这对数据中心环境尤为有利。

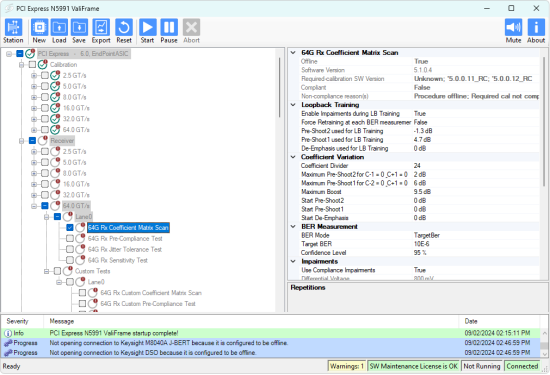

与早期的PCIe版本相比,PCIe 5.0的速度有多快?

PCIe 4.0的数据传输速率为16 GT/s,而PCIe 5则将其提高了一倍,在每个方向每个通道上传输速率都可以达到32 GT/s。就字节数而言,PCIe Gen 4 x16设备可达到32 GB/s,而PCIe 5.0可达到128 GB/s。

与PCIe 3.0的8 GT/s相比,PCIe 5每通道的吞吐量提高了四倍。

其他参数如下图所示。

图2:PCIe版本比较

每个通道在每个方向上的最大数据传输速率为32 GT/s。这相当于以下最大数据传输速率:

●x16双工PCIe插槽为128 GB/s

●x12双工为96 GB/s

●x8双工为64 GB/s

●x4双工为32 GB/s

●x2双工为16 GB/s

●x1双工为8 GB/s

PCIe 5.0设备可以在PCIe 4.0或更早版本的插槽中使用吗?

PCIe 5规范要求完全向后兼容所有早期版本。行业还可以期望PCIe 5设备具有前瞻性,能够成功兼容未来的PCIe规范,适应未来的发展要求。此外,通道数较少的PCIe设备可以安装在通道数较多的更宽的插槽中。例如,x8网卡可以安装在x16连接器中。

所有这些都可以通过协商相互兼容的通道数、PCIe版本、数据速率和编码方案等机制来实现,如下所述:

●链路训练:在链路训练期间,端点设备与根复合体进行通信。此链接初始化阶段涉及PCIe版本、数据速率、通道宽度和编码方案的协商。然后使用这些协商参数验证链接的稳定性。

●功能寄存器:PCIe设备中的功能寄存器提供有关设备支持的版本、最大通道数和其他参数的信息。

●信号:PCIe 5与所有早期版本一样使用NRZ信号。数据编码方案(如128b/130b或8b/10b)被选择为相互兼容。

PCIe 5设计中最耗时的任务是什么?

PCIe 5的高性能要求对设计和仿真阶段提出了很多需求,具体如下:

・确保信号完整性:完美的信号完整性设计至关重要。串扰、反射和模式转换是可能导致误码的重要问题,必须加以防止。

・模拟收发器合规:需要进行全面的物理层测试,以确保符合严格的标准。这需要在时域和频域进行耗时的分析和模拟。

・保持数据传输速率:高数据速率会导致管理上升时间和信号失真方面的困难。

・验证差分信号:每个PCIe通道由两对差分信号组成,一对用于发送,另一对用于接收。要在避免电磁干扰(EMI)的同时实现正确的差分信号,需要进行精心的设计和模拟。

・实现互操作性和兼容性:要确保PCIe 5端点和根复合体能够与早期版本的设备互操作,需要进行大量的模拟。

PCIe 5.0普及所面临的挑战和限制

采用PCIe 5.0所面临的挑战如下:

・信号完整性:PCIe 5等高速互连会导致阻抗不连续处的反射增加,这会降低眼图(衡量信号质量的关键指标)的质量。

・印刷电路板(PCB)设计:PCIe 5设计需要低损耗介电材料、宽信号走线以及背钻孔或微孔等技术,这些都增加了设计工作量和复杂性。

・先进仪器:PCIe 5数字设计的复杂性要求使用更精密的仪器进行分析和表征。设计工程师必须深入了解信号传播特性,并利用16-GHz矢量网络分析仪等设备对物理层组件进行全面表征。

・抖动管理:更短的时钟周期意味着更小的抖动预算。与前几代产品相比,PCIe 5减少抖动的工作更为复杂。

・回波损耗:在不同频率下保持大于特定限制的回波损耗至关重要。这涉及到精心的信道设计和合规性测试。

・接收机设计:接收机更容易受到高频信道损耗造成的信号衰减的影响。设计既能承受信号衰减,又能达到可接受误码率的强大接收机非常重要。

・协议测试:协议层内的各种状态转换以及链路训练和状态机(LTSSM)必须使用精密的仿真和测试装置进行验证。

・劳动密集型测试:PCIe 5的复杂性使得测试过程非常耗费人力。公司需要强大的自动测试解决方案,将测试时间从数天缩短至数小时。

EDA软件如何助力PCIe 5.0设计?

电子设计自动化(EDA)工具对于应对上述挑战和耗时任务至关重要。EDA软件提供助益的各种方式如下:

●信号和电源完整性模拟:随着信道拓扑的多样化和参数数量的倍增,要确保信号和电源完整性,就需要能够模拟高速集成电路和PCB互连的电磁效应的工具。EDA工具可以模拟串扰和反射等情况,以避免信号衰减和时序问题。这包括在时钟周期缩短的情况下至关重要的抖动最小化。

●信道模拟:EDA软件可创建和执行输入输出缓冲信息规范(IBIS)和算法建模接口(AMI)模型,以仿真模拟信道和端到端信号路径。

●协议层分析:EDA软件可帮助理解和优化各层――物理层、数据链路层和事务层。

●集成的协同模拟:EDA软件可同时对不同领域进行协同模拟,从而实现端到端分析。

●符合标准:EDA软件对于执行PCI-SIG要求的合规性测试至关重要。这些测试可验证电气性能是否符合PCIe 5.0标准。

●自动化测试:利用EDA工具,设计人员可将大部分测试流程自动化,以实现最高效率。合规性测试的自动化和报告的生成有助于快速验证和调整设计。

是德科技如何简化高质量PCIe 5.0设计和验证?

是德科技为深度的PCIe 5设计、仿真和测试提供了一套全面的软件解决方案和硬件设备。下文将详细介绍这些功能。

System Designer for PCIe是一种端到端设计环境,用于对PCIe 5.0系统进行建模和仿真。它通过仿真对PCIe 5.0设计执行合规性测试,可减少设计迭代,缩短产品面市时间。

System Designer for PCIe还包括IBIS-AMI建模,用于仿真电气特性和信号传输路径。

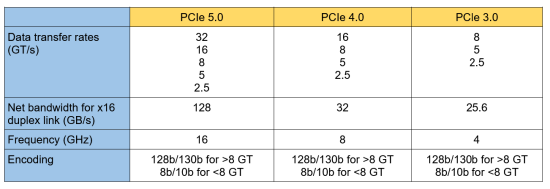

图3:是德科技接收机合规性测试自动化平台

是德科技用于PCIe 5测试的软件解决方案包括

●用于互连信号完整性测试的物理层测试系统(PLTS)

●用于验证PCIe 5接收机的N5991接收机合规性测试自动化平台

●用于测试PCIe 5发射机的发射机电气性能验证和合规性软件

这些软件支持强大的测试和验证功能,如以下所列:

・它们有助于进行时域和频域分析,使工程师能够准确评估信号完整性。

・批处理模式的自动夹具移除支持使用单个夹具模型进行多通道去嵌入,大大缩短了分析时间。

・模式转换分析可帮助及早发现与EMI和系统性能有关的潜在问题。

・虚拟伪随机比特序列模式发生器可加快根据S参数生成眼图的速度,将通常的处理时间从数小时缩短到数秒。

・它们可以对传输线进行高精度的表征,以仿真和改善信号完整性。

协议分析

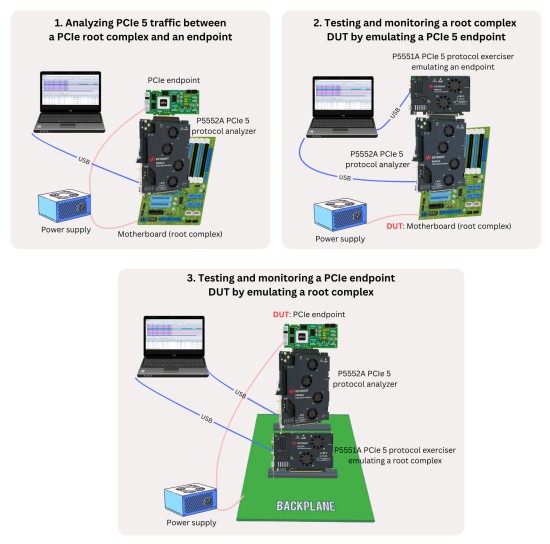

图4:使用是德科技分析仪和训练器进行PCIe 5协议分析

PCIe 5协议训练器和协议分析仪可对所有拓扑和用例进行分析。

通过是德科技加快PCIe 5设备的面市速度

本文已概括性地叙述了PCIe 5所面临的挑战以及应对这些挑战的解决方案。

欢迎联系是德科技,了解如何使用是德科技的硬件和软件解决方案,将PCIe 5设备快速、高质量地推向市场。

1.本网刊载内容,凡注明来源为“飞象网”和“飞象原创”皆属飞象网版权所有,未经允许禁止转载、摘编及镜像,违者必究。对于经过授权可以转载,请必须保持转载文章、图像、音视频的完整性,并完整标注作者信息和飞象网来源。

2.凡注明“来源:XXXX”的作品,均转载自其它媒体,在于传播更多行业信息,并不代表本网赞同其观点和对其真实性负责。

3.如因作品内容、版权和其它问题,请在相关作品刊发之日起30日内与本网联系,我们将第一时间予以处理。

本站联系电话为86-010-87765777,邮件后缀为cctime.com,冒充本站员工以任何其他联系方式,进行的“内容核实”、“商务联系”等行为,均不能代表本站。本站拥有对此声明的最终解释权。

5G-A赋能机器人火炬接力:中国移动以技术革新点亮全运科技盛宴

2025年11月,第十五届全国运动会将在粤港澳三地盛大启幕。这场赛事不仅是体育健儿的竞技场,更是前沿科技落地应用的“试验田”。其中,11月2日的机器人火炬接力作为本次全运会的核心创新亮点..[详细]

轻薄机型出师未捷身先死,长使业绩泪满襟

当iPhone Air宣布上市当天,随着各路评测内容解禁,一个显眼的标题也随之出现,那就是“注定停产”。轻薄机型的出现一方面让人们看到厂商正在挖掘全新市场空间,另一方面也勾起了小尺寸机型..[详细]

智能未来:宇宙为你闪烁

未来十年,你家的电表可能再也不用换电池,自动驾驶汽车能"看到"几公里外的路况,甚至海洋深处的传感器都能实时传回数据。这些不是科幻,而是刚刚在无锡物博会上发布的《2025全球..[详细]

智能IP广域网成为筑牢智算产业发展根基的关键一环

随着国家加速推动智算产业高质量发展,网络支撑能力已成为产业进阶的核心抓手,而作为关键基础设施的智能IP广域网,正凭借其在算力调度、数据传输中的核心作用,成为筑牢智算产业发展根基的..[详细]

大中华区市场失守 苹果寄望AI驱动未来增长

苹果公司公布的2025 财年第四季度财报呈现“冰火两重天”态势:全球营收1024.66亿美元同比增长 8%,净利润274.66亿美元同比激增86.4%,毛利率攀升至 47.18%。但作为第三大市场的大中华区却成..[详细]